环栅器件无损检测技术研究获得新突破

浏览量:742次发布时间:2022年10月17日

随着先进制造工艺的复杂程度和精细程度越来越高,为了保证生产良率,对关键工艺步骤进行在线检测变得越来越重要。FinFET技术之后的环栅器件的沟道应力和完整性决定了最终器件的性能,同时也可以反映出制造流程中的工艺健康程度。因此,构建在线无损检测能力是环栅器件中的一个关键技术。

现有相关技术中,在制备半导体器件的过程中,可采用XRD(X射线衍射仪)对应力进行测试,从而表征出应力水平。也可采用TEM(透射电子显微镜)对应力进行测试,从而表征出应力水平。然而,XRD的光斑面积较大,适用于较大范围的测量。但是,环栅器件的特征尺寸远远小于XRD的光斑,因此XRD难以做到准确的测量。同时,TEM易于对测试对象造成损伤。可见,现有技术中,无法在无损的情况下准确对环栅器件中的沟道应力进行测试与表征。

针对上述问题,来自国家集成电路创新中心/复旦大学微电子学院的张卫/徐敏团队发明了一种环栅器件制备的测试方法与系统,并申请了中国发明专利(专利公开号:CN113964202A)。

在本专利所公开的技术方案中,将拉曼测试装置引入到环栅器件制备的工艺环节。进而能够在生长外延层后、刻蚀鳍片后、源漏外延(且伪栅极被去除)、释放牺牲层后、HKMG包裹沟道后等至少之一时间点对沟道对应位置的应力进行测试;在此基础上,测试结果可反应出沟道对应位置应力随制备工艺环节的变化。其中,由于拉曼测试装置的测试光的光斑面积较小,从而可在测试中表征出较小尺寸的结构应力。同时,在该过程中,也不会对样品表面产生损伤。因此,本发明能够在无损的情况下准确对各工艺环节下沟道对应位置的应力进行测试与表征,为制备工艺的进一步分析与改进提供准确、充分的依据。也就是说,本发明相比于已知的测试方法具有明显的创造性和技术先进性。

为了进一步验证上述专利所提出的技术方案具有可实施性和多方面应用性,研究团队基于共聚焦拉曼测试系统,结合DTCO技术,在自主开发的环栅晶体管工艺流程中,实现了沟道应力的无损检测,并且展示了该应力表征技术在检测器件沟道完整性上的可能性。相关工作以 “A Non-Destructive Channel Stress Characterization for Gate-All-Around Nanosheet Transistors by Confocal Raman Methodology”发表于National Science Open。复旦大学微电子学院博士生黄自强为第一作者,张卫教授、徐敏研究员、王晨副教授为共同通讯作者。

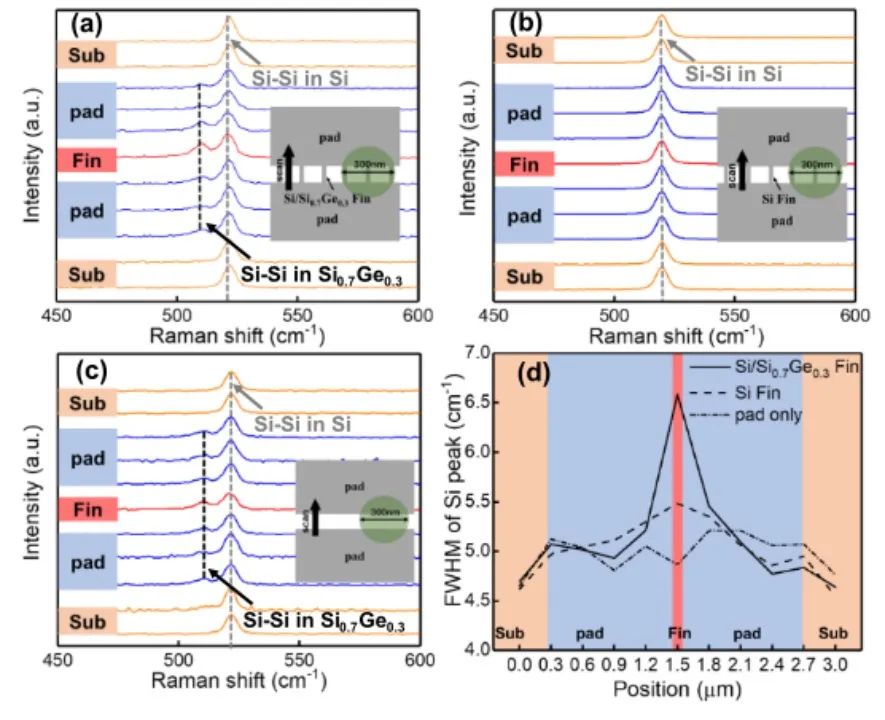

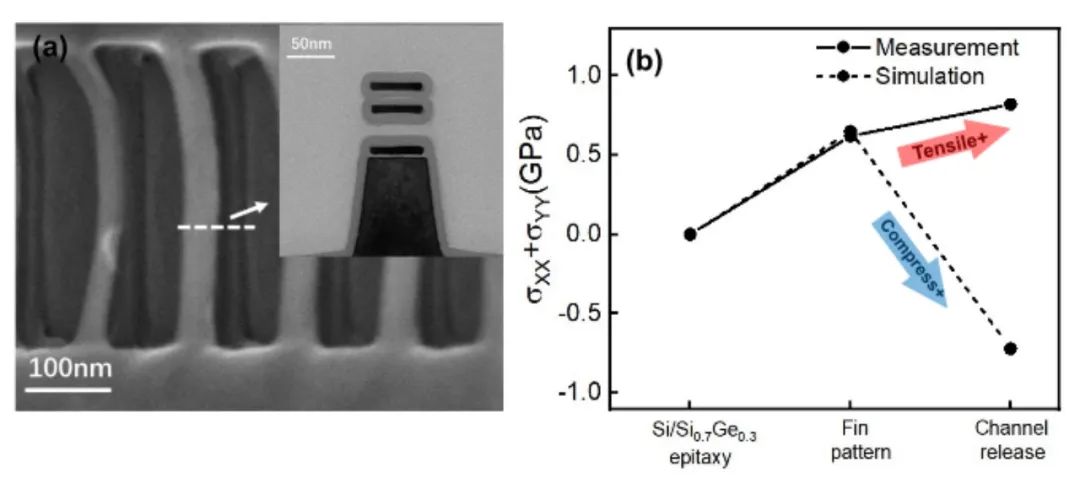

通过设计高密度排列的纳米线沟道提高测试的信噪比,同时对比分析不同结构下的线扫拉曼光谱,可以有效地表征出纳米尺度下的纳米片沟道中应力硅峰的展宽(图1)。应用此方法,成功得到了环栅器件制备过程中应力的演变曲线,并且与DTCO仿真数据相吻合(图2)。此外,文中还展示了通过应力测试来反映制造工艺良率的可能性。在沟道存在缺陷的环栅器件中,沟道应力会偏离理想行为(图3),这一表征信息可为沟道工艺良率提供关键信息反馈。该方法也使得环栅器件中源漏外延的在线缺陷检测成为可能。

图1 不同结构纳米片的线扫拉曼光谱和Si-Si半峰宽

图2 环栅器件制备过程中的沟道应力演变和应力传递机理

图3 有缺陷的纳米片沟道中,沟道应力的演变偏离理想情况

来源:国家集成电路创新中心